KNS 2013 Spring 광주 김대중컨벤션센터 2013.5.29 ~ 2013.5.31

# Equivalence Checking between Pre-synthesis and Post-synthesis Programs by Using VIS Jong-Hoon Lee Dependable Software Laboratory Konkuk University

## Introduction

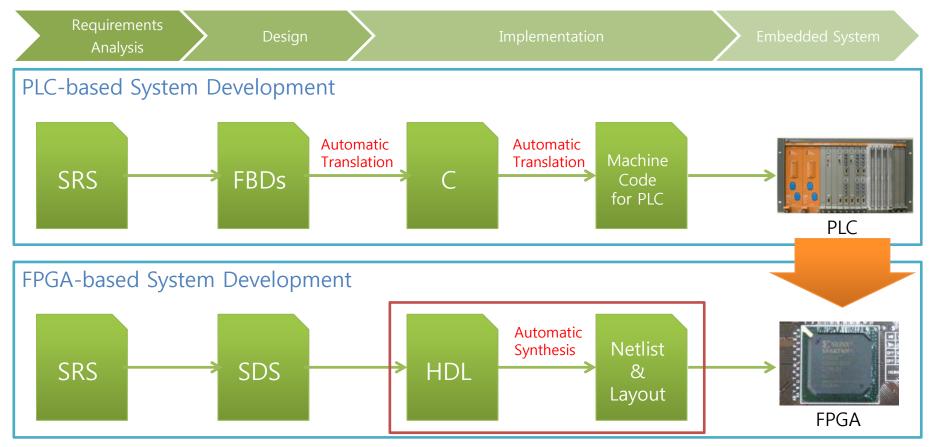

- Platform Change from PLC to FPGA in Nuclear Industry

- Behaviorally Equivalence between Outputs is required

- Formal Method based Techniques

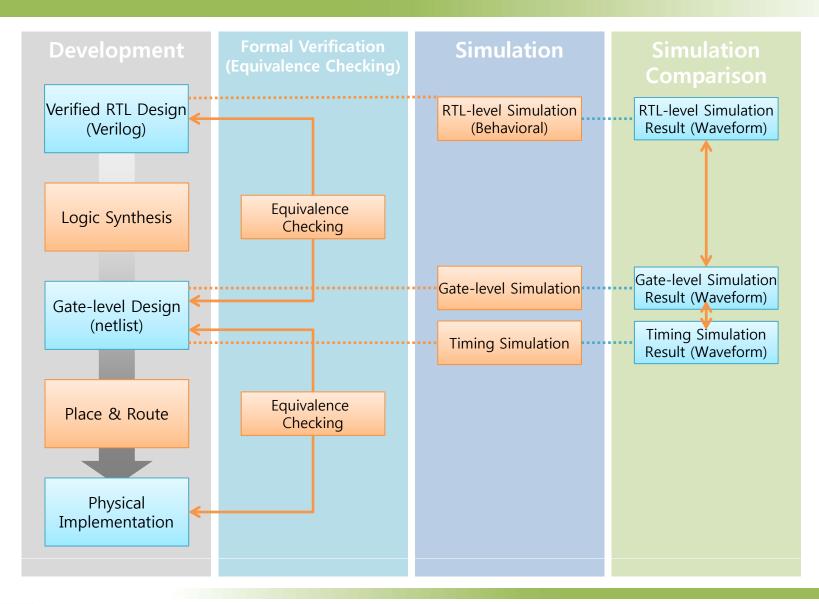

## Verifications in FPGA

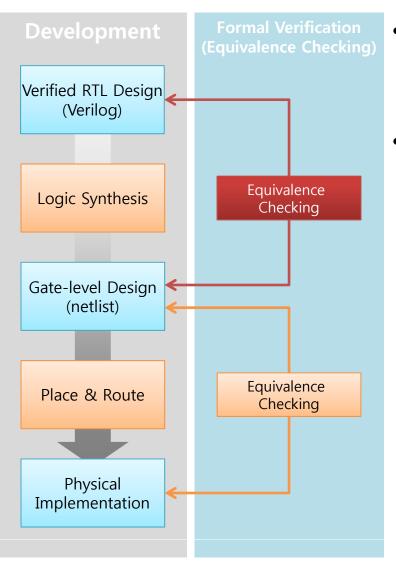

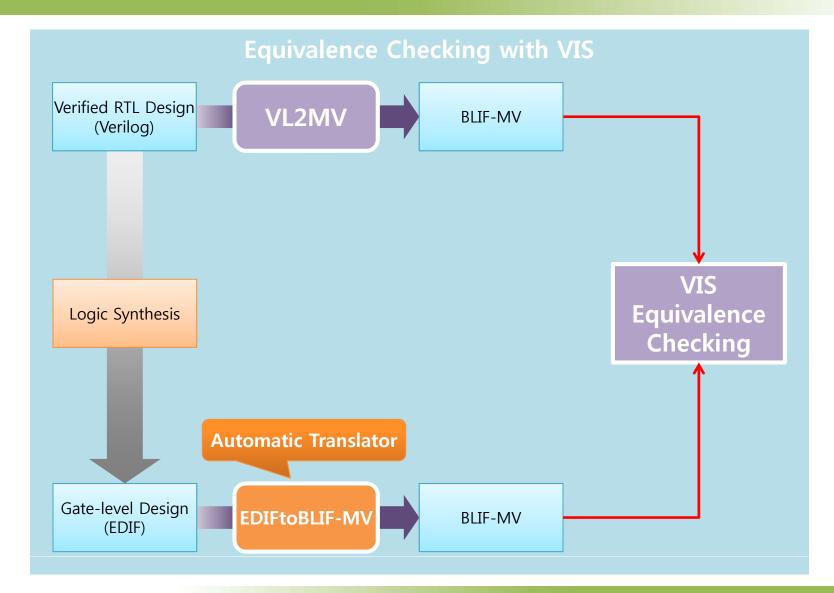

## **Equivalence Checking with VIS**

- Equivalence Checking is required

- Equivalence Checking between Designs

- VIS Verification System

- Developed by

Univ. of California at Berkeley,

Univ. of Colorado at Boulder and

Univ. of Texas

- It has Equivalence Checking feature

- It reads BLIF-MV modeling language

- It only supports Verilog format

## **Equivalence Checking with VIS**

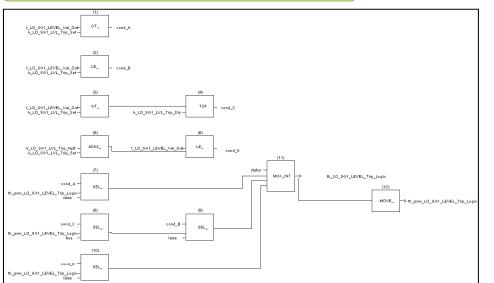

## **EDIFtoBLIF-MV**

- Translation Rule

- We defined translation templates

- Translate into BLIF-MV from EDIF using defined rules

|     | EDIF                                                                                                                                                                                                                                       | BLIF-MV                                                                                                                                                 | Description                                                                 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 1-1 | (cell <name_of_cell><br/></name_of_cell>                                                                                                                                                                                                   | .model ⊲name_of_cel⊳<br><br>.end                                                                                                                        | Cell in work library<br>Translate to '.model'                               |

| 1-2 | (cell <name_of_cell><br/>(view</name_of_cell>                                                                                                                                                                                              | .names <1nput> ··· <output><br/>.def 0<br/><truth_table_of_functionality></truth_table_of_functionality></output>                                       | 'combinational' cell in<br>external library<br>Translate to truth table     |

| 1-3 | (cell <name cell="" of=""><br/>(property is sequential (1))<br/>(view<br/>(interface<br/>(port <name_of_port><br/>(direction <input output=""/>)<br/>(property function (<functionality>)<br/>)<br/></functionality></name_of_port></name> | .r <reset><br/>.def 0<br/>Jatch <input/> <output></output></reset>                                                                                      | 'sequential' cell in<br>external library<br>Translate to '.latch'           |

| 2   | (cell <name_of_cell><br/>(view<br/>(interface<br/>(port <name_of_port><br/>(direction &lt;1nput/Output&gt;)<br/>)</name_of_port></name_of_cell>                                                                                            | .model <name_of_cell><br/>.inputs <input/> <input/><br/>.outputs <output> <output><br/><br/>.end</output></output></name_of_cell>                       | Ports in Cell in work library<br>Translate to '.inputs'<br>and/or 'outputs' |

| 3-1 | (cell<br>(view<br>(contents<br>(instance <name_of_instance><br/>(viewRef <name_of_referred_view><br/>(cellRef <name_of_referred_cell><br/></name_of_referred_cell></name_of_referred_view></name_of_instance>                              | .names <input/> ··· <output><br/>.def0<br/><truth_table_of_functionality_of_referre<br>d_cell&gt;</truth_table_of_functionality_of_referre<br></output> | Instance which refer to<br>'combinational' cell                             |

| 3-2 | (cell<br>(view<br>(contents<br>(instance <name_of_instance><br/>(viewRef <name_of_referred_view><br/>(cellRef <name_of_referred_cel><br/></name_of_referred_cel></name_of_referred_view></name_of_instance>                                | .r <reset><br/>.def 0<br/>.latch <input/> <output></output></reset>                                                                                     | Instance which refer to<br>'sequential' cell                                |

| 3-3 | (cell<br>(view<br>(contents<br>(instance <name_of_instance><br/>(viewRef <name_of_referred_view><br/>(cellRef <name_of_referred_cel><br/></name_of_referred_cel></name_of_referred_view></name_of_instance>                                | subckt ⊲name_of_referred_cel⊳<br>⊲name_of_instance> ⊲Input> …<br>⊲Output> …<br>                                                                         | Instance which refer to<br>other cell in work library                       |

| 3-4 | (cell<br>(view<br>(contents<br>(net ~name_of_net> (joined<br>(portRef ~Input_Port><br>(instanceRef<br><name_of_input_instance>))<br/></name_of_input_instance>                                                                             | .names <name_of_input_instance><br/><name_of_output_instance><br/>.def0<br/>1 1</name_of_output_instance></name_of_input_instance>                      | Network connection between cells                                            |

## • A part of translation rule

| Rule | EDIF                                                                                                                                                                                                                                                            | BLIF-MV                                                                                                            | Description                                                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 1-1  | (cell <name_of_cell><br/></name_of_cell>                                                                                                                                                                                                                        | .model <name_of_cell><br/><br/>.end</name_of_cell>                                                                 | Cell in work library<br>Translate to '.model'                           |

| 1-2  | <pre>(cell <name_of_cell> (view  (interface    (port <name_of_port>      (direction <input output=""/>)      (property function (<functionality>)    )</functionality></name_of_port></name_of_cell></pre>                                                      | .names <input/> ··· <output><br/>.def 0<br/><truth_table_of_functionality></truth_table_of_functionality></output> | 'combinational' cell in<br>external library<br>Translate to truth table |

| 1-3  | <pre>(cell <name_of_cell>  (property is_sequential (1))  (view     (interface        (port <name_of_port>        (direction <input output=""/>)        (property function (<functionality>)        )       </functionality></name_of_port></name_of_cell></pre> | .r <reset><br/>.def 0<br/>.latch <input/> <output></output></reset>                                                | 'sequential' cell in<br>external library<br>Translate to '.latch'       |

A part of KNICS RPS BP Logic (*th\_LO\_SG1\_LEVEL\_Trip*)  ${\color{black}\bullet}$

It consist of 6 shutdown logic (792 FB) We only used 17 FB

#### Verilog HDL module th LO SG1 LEVEL Trip Logic(clk, reset, f LO SG1 LEVEL Val Out, input clk; input reset; input [15:0] f\_LO\_SG1\_LEVEL\_Val\_Out; output th\_LO\_SG1\_LEVEL\_Trip\_Logic; wire cond A; wire cond B; wire cond C; wire cond D; wire [15:0] status; reg [15:0] prev status; initial prev status = 16'b00000000000000; cond A th LO SG1\_LEVEL Trip\_Logic th LO SG1\_LEVEL\_Trip\_Logic M1(clk, cond\_B\_th\_L0\_SG1\_LEVEL\_Trip\_Logic th\_L0\_SG1\_LEVEL\_Trip\_Logic\_M2(clk, cond C th LO SG1 LEVEL Trip Logic th LO SG1 LEVEL Trip Logic M3(clk, cond D th LO SG1 LEVEL Trip Logic th LO SG1 LEVEL Trip Logic M4(clk, th\_LO\_SG1\_LEVEL\_Trip\_Logic\_Processing\_th\_LO\_SG1\_LEVEL\_Trip\_Logic\_th\_I status th LO SG1 LEVEL Trip Logic th LO SG1 LEVEL Trip Logic M6(clk, always @(posedge clk) begin if(reset) begin prev status = 16'b00000000000000; end else begin prev status = status; $\mathbf{end}$ end endmodule module cond\_A\_th\_LO\_SG1\_LEVEL\_Trip\_Logic(clk, f\_LO\_SG1\_LEVEL\_Val\_Out // input, output variables input clk; input [15:0] f LO SG1 LEVEL Val Out; input [15:0] k LO SG1 LVL Trip Set; output out;

### EDIF

| <pre>(edifVersion 2<br/>(edifLevel 0)<br/>(keywordMap (k<br/>(status<br/>(written<br/>(timeStamp<br/>(author "S<br/>(program "<br/>)<br/>)<br/>(library PA3<br/>(edifLevel 0<br/>(technology<br/>(cell XAIA (<br/>(property<br/>(view pri</pre> | <pre>seywordLevel 0))<br/>2 2013 3 1 20 11 53)<br/>ynopsys, Inc.")<br/>Synplify Pro" (version "E-2010.09A-1, m<br/>(numberDefinition ))<br/>cellType GENERIC)<br/>dont_touch (string "false"))<br/>m (viewType NETLIST)<br/>face<br/>: Y (direction OUTPUT)<br/>: A (direction INFUT)<br/>: B (direction INFUT)<br/>: C (direction INFUT)<br/>: C (direction INFUT)<br/>: y is_combinational (integer 1))<br/>:ellType GENERIC)<br/>dont_touch (string "false"))<br/>m (viewType NETLIST)<br/>:===<br/>: Y (direction OUTPUT)<br/>: ellType GENERIC)<br/>dont_touch (string "false"))<br/>m (viewType NETLIST)<br/>:===<br/>: Y (direction OUTPUT)<br/>: ellType GENERIC)<br/>: direction OUTPUT)<br/>: ellType GENERIC)<br/>: for the term of the term of the term of the term of ter</pre> |                     | Translation | <pre># cell th_LO_SG1_LEVEL_Trip_Logic<br/>.model th_LO_SG1_LEVEL_Trip_Logic<br/># interface - I/O ports<br/>.inputs reset f_LO_SG1_LEVEL_Val_Out<o><br/>.outputs th_LO_SG1_LEVEL_Trip_Logic<br/>.names N_16SM6 N_10\$M6 reset_pad prev_s<br/>.def 0<br/>0 0 0 1<br/>0 1 0 1<br/>1 0 0 1<br/># latches<br/># init<br/>.r prev_status_0<br/>.def 0<br/>.latch prev_status_RNO_0 prev_status_0<br/>.names N_5\$M5 th_LO_SG1_LEVEL_Trip_Logi<br/>.def 0<br/>1 1<br/>.names f_LO_SG1_LEVEL_Val_Out&lt;15&gt; f_LO_<br/>.def 0<br/>1 1<br/>.names f_LO_SG1_LEVEL_Val_Out&lt;15&gt; f_LO_<br/>.def 0<br/>1 1<br/>.names f_LO_SG1_LEVEL_Val_Out&lt;14&gt; f_LO_<br/>.def 0<br/>1 1<br/>.names f_LO_SG1_LEVEL_Val_Out&lt;13&gt; f_LO_<br/>.def 0<br/>1 1<br/>.names f_LO_SG1_LEVEL_Val_Out&lt;12&gt; f_LO_<br/>.def 0<br/>1 1<br/>.names f_LO_SG1_LEVEL_Val_Out&lt;11&gt; f_LO_<br/>.def 0<br/>1 1<br/>.names f_LO_SG1_LEVEL_Val_Out&lt;10&gt; f_LO_<br/>.def 0<br/>1 1<br/>.names f_LO_SG1_LEVEL_Val_Out&lt;10&gt; f_LO_<br/>.def 0<br/>1 1</o></pre> | status_RNO_0<br>ic_pad<br> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                                                                                                                                                                                                                                 | Verilog HDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | EDIF                |             | BLIF-MV from Verilog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BLIF-MV from EDIF          |

| LoC                                                                                                                                                                                                                                             | 288                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1210                |             | 4944                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 344                        |

| Node                                                                                                                                                                                                                                            | 8 modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2 librar<br>7 cells | ies         | 24 models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7 models                   |

**BLIF-MV**

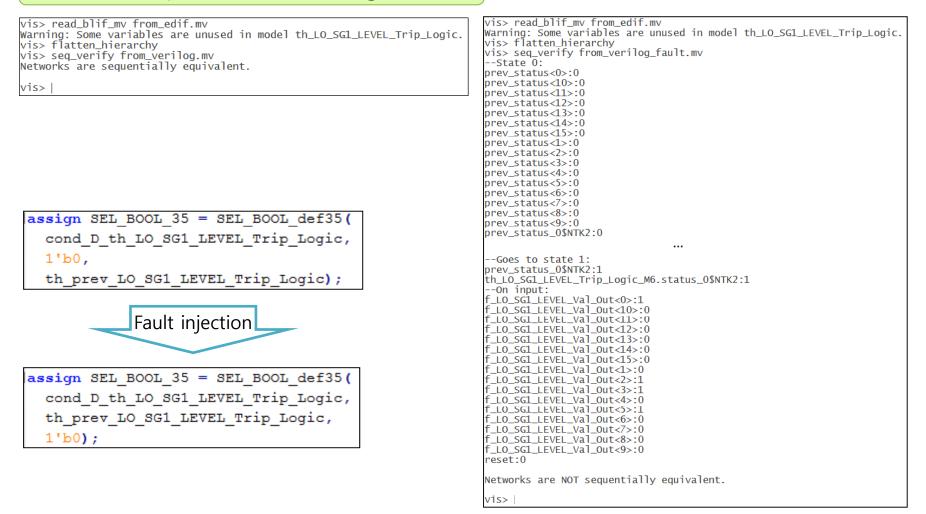

## Results of Equivalence Checking with VIS

## **Conclusion and Future Work**

- Confirmation of Correctness of Synthesis

- Formal Method based Technique (Equivalence Checking)

- Automatic Program Translation

- Translate into BLIF-MV from EDIF

- EDIF: Gate-level netlist format of EDA tools

- BLIF-MV: Front-end format of VIS

- Future Work

- Formalize the translation rule

- A whole set of KNICS RPS BP Logic

- Equivalence Checking between Gate-level Design and Physical Layout

#